| 数字逻辑实验:同步模4可逆计数器 | 您所在的位置:网站首页 › verilog jk触发器 › 数字逻辑实验:同步模4可逆计数器 |

数字逻辑实验:同步模4可逆计数器

|

一、实验目的和任务

实验目的

掌握同步时序逻辑电路的设计方法,验证设计的同步时序逻辑电路,加深对同步和时序两个概念的理解。 实验任务 用D触发器74HC74(实验使用74HC175代替)和74HC86设计制作一个模4可逆计数器。 关键词:同步时序电路 模4可逆计数器 二、芯片74HC175和74HC86 74HC175

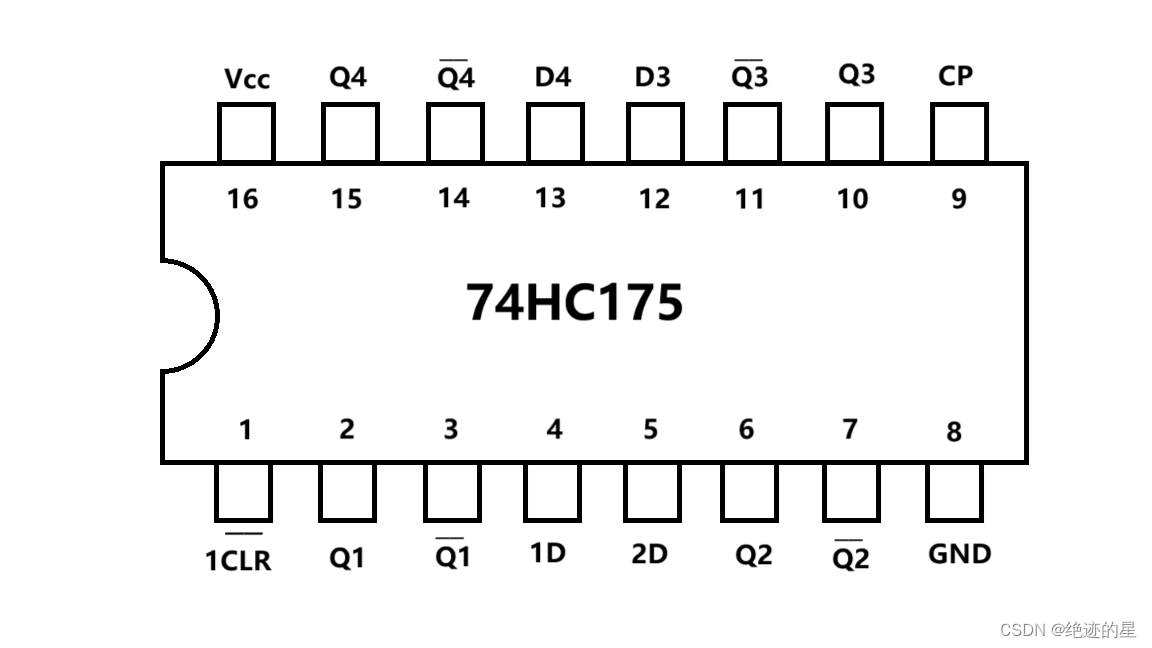

(在智力抢答器一章使用过74HC175) 74HC175是4位D触发器,Q=D Vcc接电源,GND接地D为输入端Q为输出端CLR为清零端,低电平生效,当输入低电平时,芯片输出信号全为0CP接入时钟脉冲,上升沿触发,当接收到高电平脉冲时,D输入端的数据被转移至Q输出端,并在Q输出端保持不变,直到下一个高电平脉冲(74HC74是2位D触发器,因为实验任务是4人抢答器,如果使用74HC74则需要2片,所以为了简化,改用74HC175芯片) 74HC86

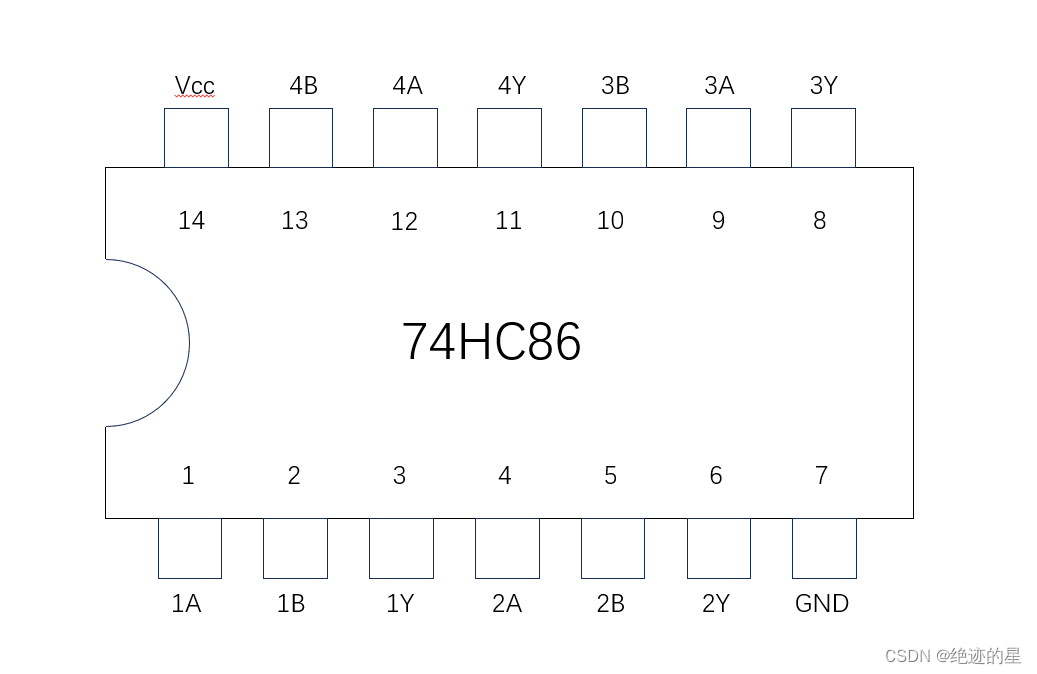

74HC86是四通道二输入异或门,实现功能Y=A⊕B Vcc接电源,GND接地A和B为输入端Y为对应输出端,Y=A⊕B 三、同步模4可逆计数器 ①要求实现以4为模的递增计数以及递减计数功能 当输入信号x=0时减1计数,当输入信号x=1时加1计数 循环计数末端有进位输入或借位输出 器件:D触发器74HC74(175)和74HC86和必要的与非门等。 ②状态表和状态图模四计数,0,1,2,3可以用两个二进制位存储 输入信号为x, 当前计数为 输出信号为Z表示进位和借位信息, 当计数由11->00正溢出时输出1, 当00->11负溢出时输出1 现态次态

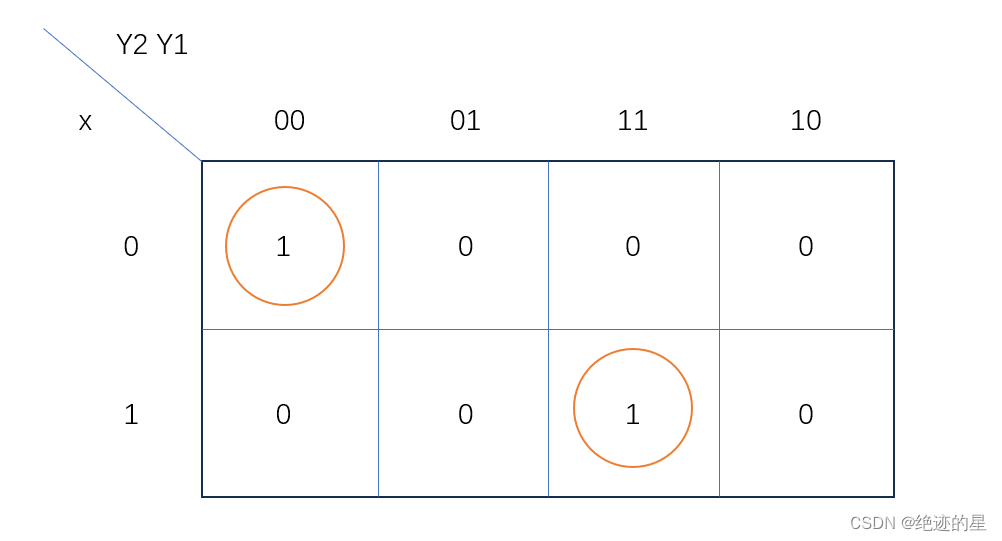

74HC175是D触发器, 所以根据 状态 和 D触发器的激励表 画出激励函数 D触发器的状态转移方程为

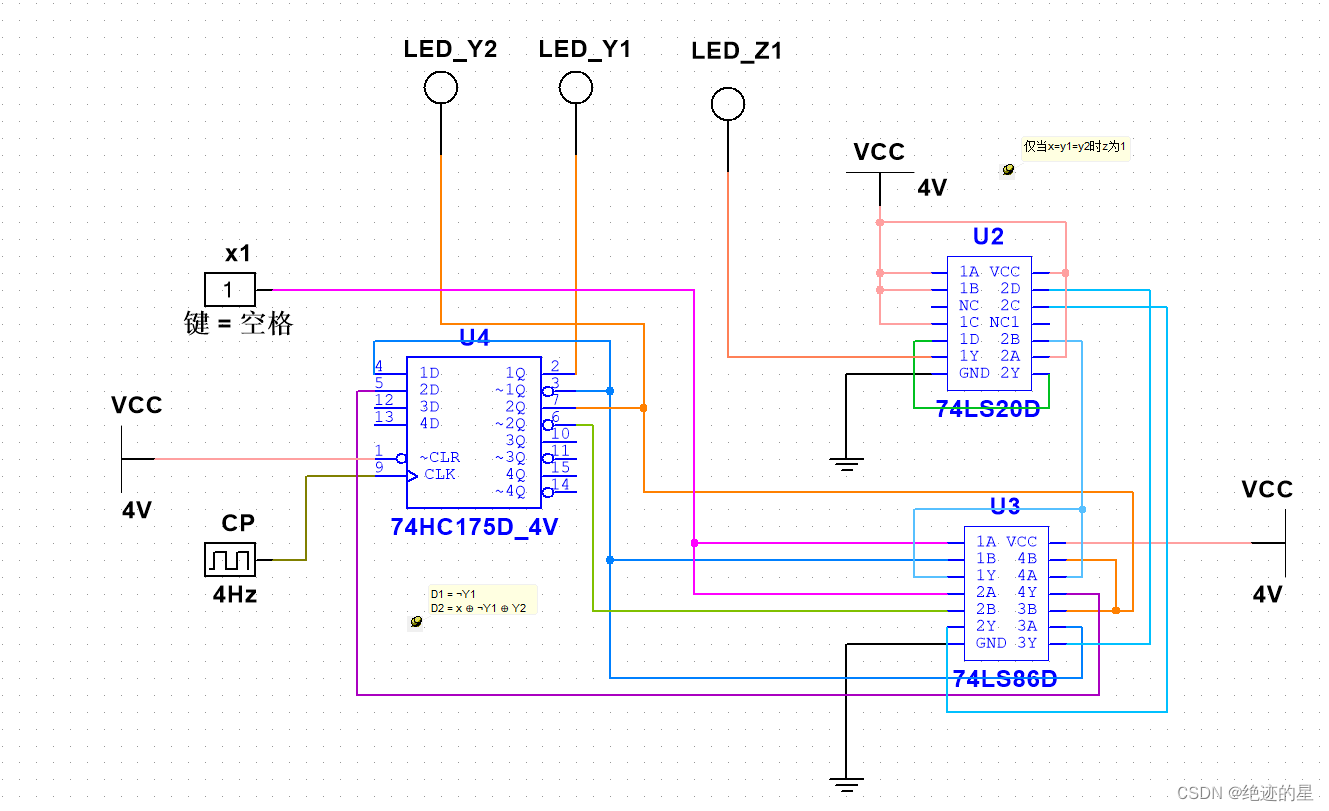

关于Z的输出部分(x=y1=y2时输出1, Z = x y1 y2), 由于实验限制只能使用与非门, 所以先将 x、y1、y2做与非运算, 再取反即可得到x、y1、y2的与 非门可以通过与非门改编: 1和X与非 → X的非

补充: 74LS20不使用的端口应该接1而不是悬空, 网上说悬空默认是1, 但经过测试, 悬空值为0, 会导致输出一直为1 点击获取Multisim安装包 |

【本文地址】

公司简介

联系我们